先来看一下什么是 DDR。DDR(Double Data Rate)属于SDRAM(Synchronous Dynamic Random Access Memory)的一种。DDR 的主要特点是数据传输速率更高。DDR 内存采用了一种称为“双倍数据速率”的技术,它可以在一个时钟周期内传输两次数据,即在时钟信号的上升沿和下降沿都能进行数据传输。而普通的 SDRAM 在一个时钟周期内只能在上升沿或者下降沿传输一次数据。

DDR5 是第五代 DDR 技术,核心技术参数如下:

-

发布年份:2020

-

数据速率:4800-6400 MT/s (未来有潜力达到更高速度)

-

带宽:38.4-51.2 GB/s

-

电压:1.1V (更低功耗)

-

密度:每颗 IC 高达 64 Gb

-

通道配置:每 DIMM 双通道 (有效将可用通道数加倍)

-

预取缓冲区:16n (DDR4 的两倍)

-

延迟:低于 DDR4

-

提升的通道效率:双通道带来更高效的数据传输

-

更佳的电源管理:芯片内置 ECC (错误修正码) 提升可靠性与性能

-

改善的信号完整性:新功能如决策反馈均衡 (DFE)

总结一下 DDR5 的特点:

-

速度与带宽:DDR5 提供比 DDR4 高出许多的数据速率与带宽。

-

电源效率:DDR5 运作电压更低,从而降低功耗。

-

密度与容量:DDR5 支持更高密度,允许更大的内存容量。

-

通道配置:DDR5 的每 DIMM 双通道设计提升了通道效率。

-

先进功能:DDR5 包含芯片内置 ECC 和改善的信号完整性机制等先进功能。

LPDDR5(Low Power Double Data Rate 5)是一种专门为移动设备和功耗敏感型设备(如智能手机、平板电脑、轻薄本)设计的内存标准。

它的核心特性是“低功耗”。它通过使用更低的工作电压(例如 1.05V 核心电压和 0.5V I/O 电压)和更先进的电源管理功能,来实现极高的能效,从而最大限度地延长设备的电池续航时间。

虽然两者都是“DDR5”家族的成员,但它们在设计理念、物理形态和性能侧重上有根本的不同。

| 特性 | LPDDR5 (Low Power DDR5) | DDR5 (Standard DDR5) |

| 主要应用 |

|

|

| 设计目标 | 低功耗、延长电池续航、小体积 | 高性能、高带宽、高容量 |

| 物理形态 | 焊接在主板上(BGA 封装),呈小方块芯片状 | 插槽式内存条,可更换和升级 |

| 功耗与电压 | 极低。工作电压更低且通常是动态可变的(例如 1.05V / 0.5V) | 较低(相比 DDR4)。标称电压通常为 1.1V |

| 通道架构 |

|

|

| 性能 |

|

|

DDR5 与之前版本 DDR 对比

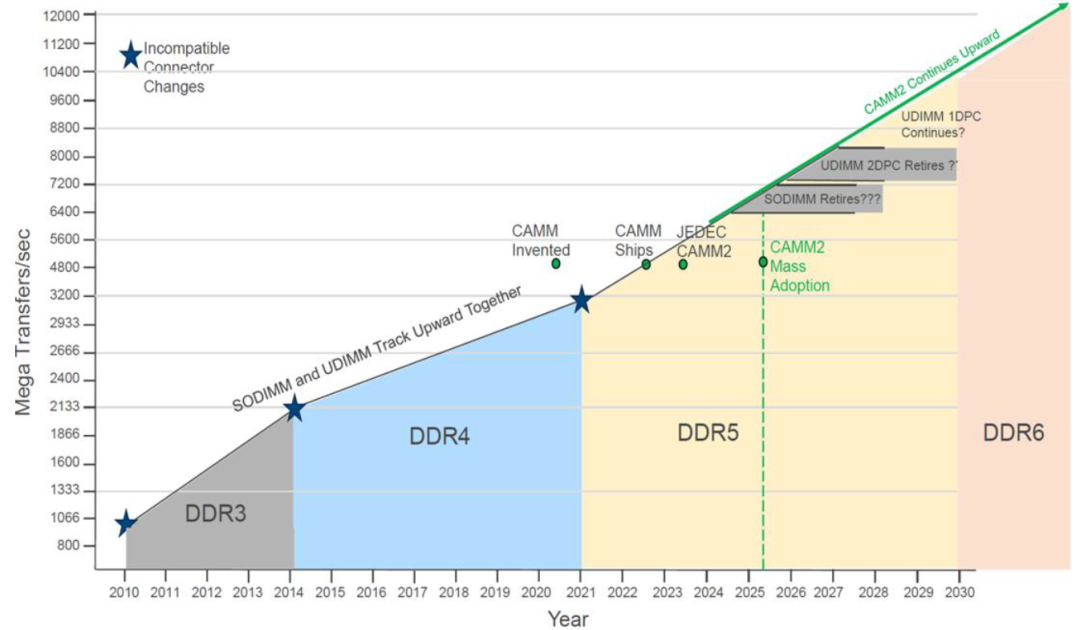

下图是 DDR 进化的图表:

可以看到,JEDEC 在 2021 年的时候发布了 CAMM2 模组,尝试解决 SODIMM 的系统级问题,CAMM2 从性能、尺寸、布线难度、可替换性、EMC 噪声等多方面进行了改进,后续章节会详细介绍。

下表是 DDR5 和之前 DDR 版本的一个比较:

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

我们来回顾一下 DDR 的发展历史:

-

由 IBM 于 1980 年代发明

-

1990 年在国际固态电路研讨会上发表

-

三星于 1998 年 6 月发布首款商用 DDR SDRAM 芯片 (64 Mbit)

-

JEDEC 于 2000 年 6 月敲定规格 (JESD79)

-

首款使用 DDR SDRAM 的零售 PC 主板于 2000 年 8 月发布

-

DDR1 (2000): 在时钟的上升沿和下降沿皆传输数据,速率加倍

-

DDR2 (2003): 改善的 I/O 总线信号,双通道模式

-

DDR3 (2007): 增加的带宽,降低的功耗

-

DDR4 (2014): 四点时钟周期数据传输,高效的 DRAM Bank 组

-

DDR5 (2022): 更佳的电源管理,提升的通道效率,更强的性能

-

CAMM2 模组(2024)

-

LPDDR5 CAMM2(2024):低功耗DDR5

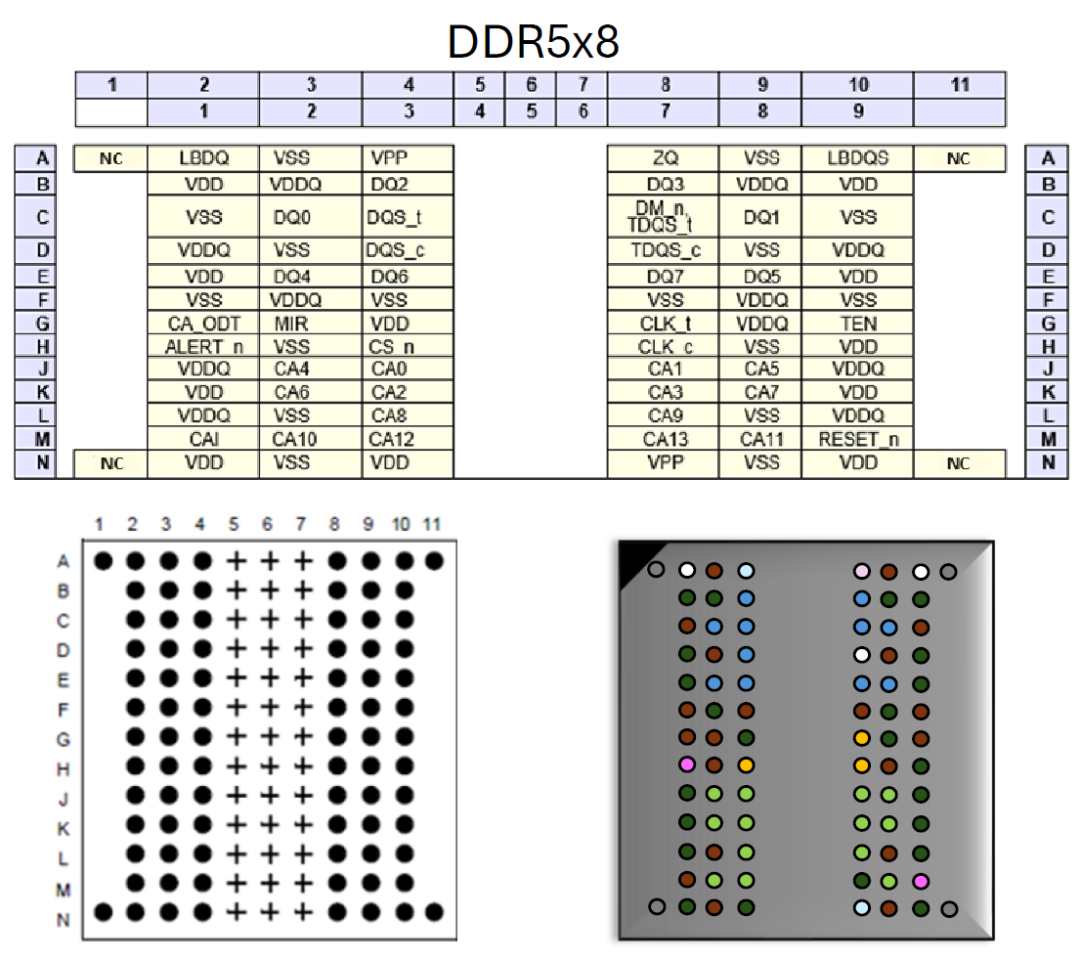

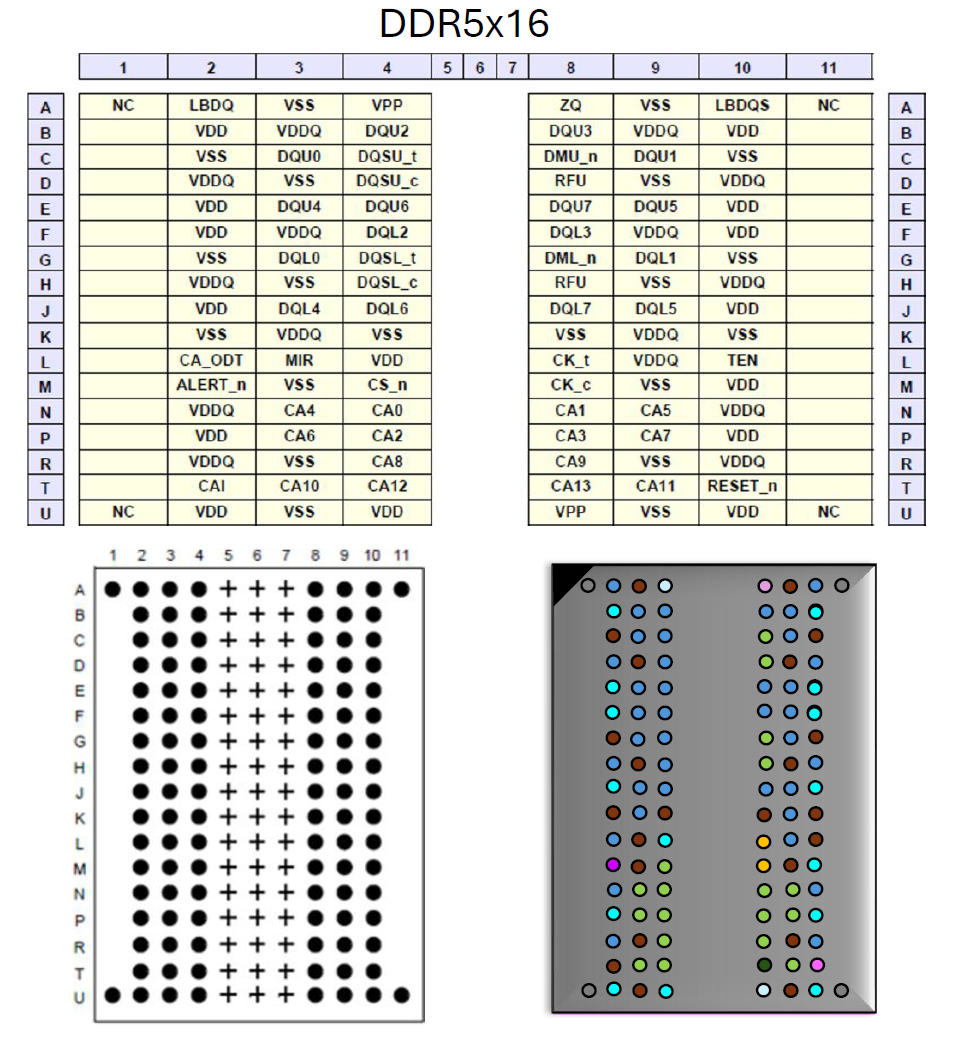

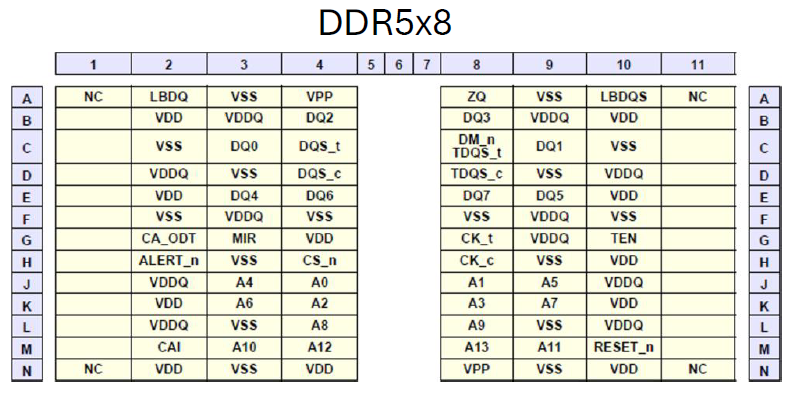

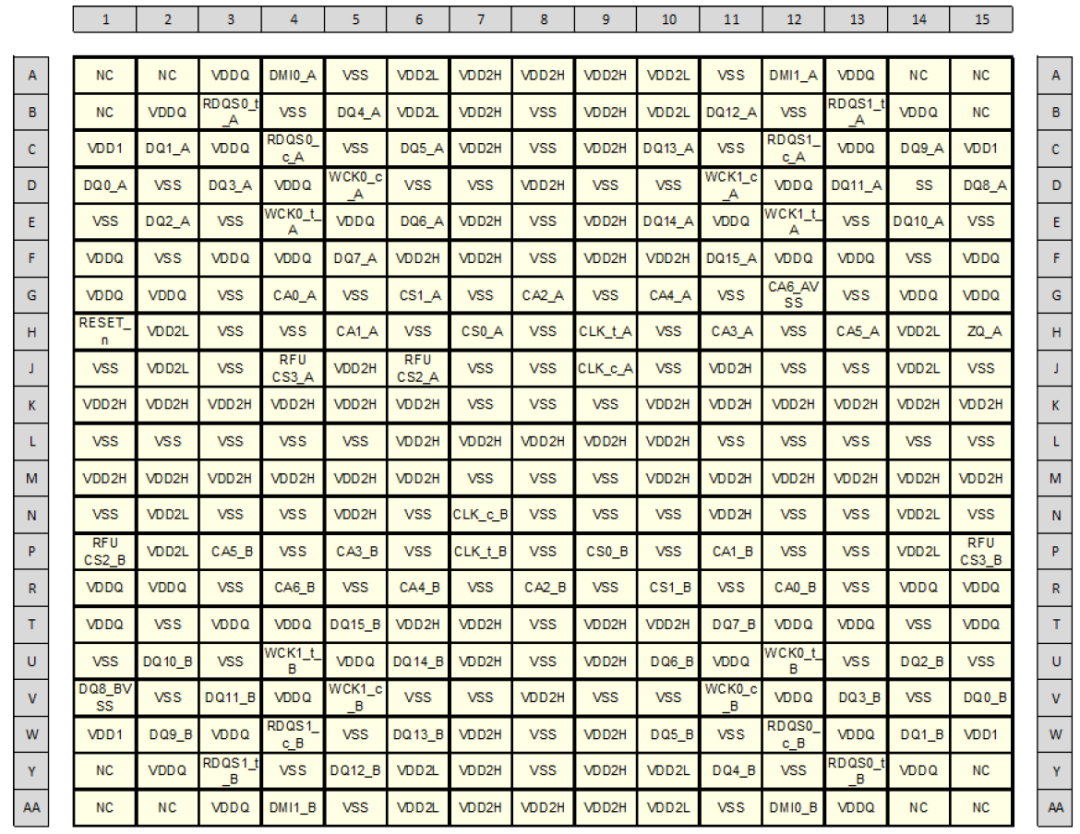

DDR5 DRAM 引脚

8位数据位宽的封装由 82 个 ball 组成,尺寸最大为 10mm x 11mm x 1 mm。上图右下为顶视图(右图为从定向下穿透视角)。做下中“+”表示没有 Ball。

16位数据位宽的封装由 106 个 ball 组成,尺寸最大为 10mm x 14mm x 1mm。

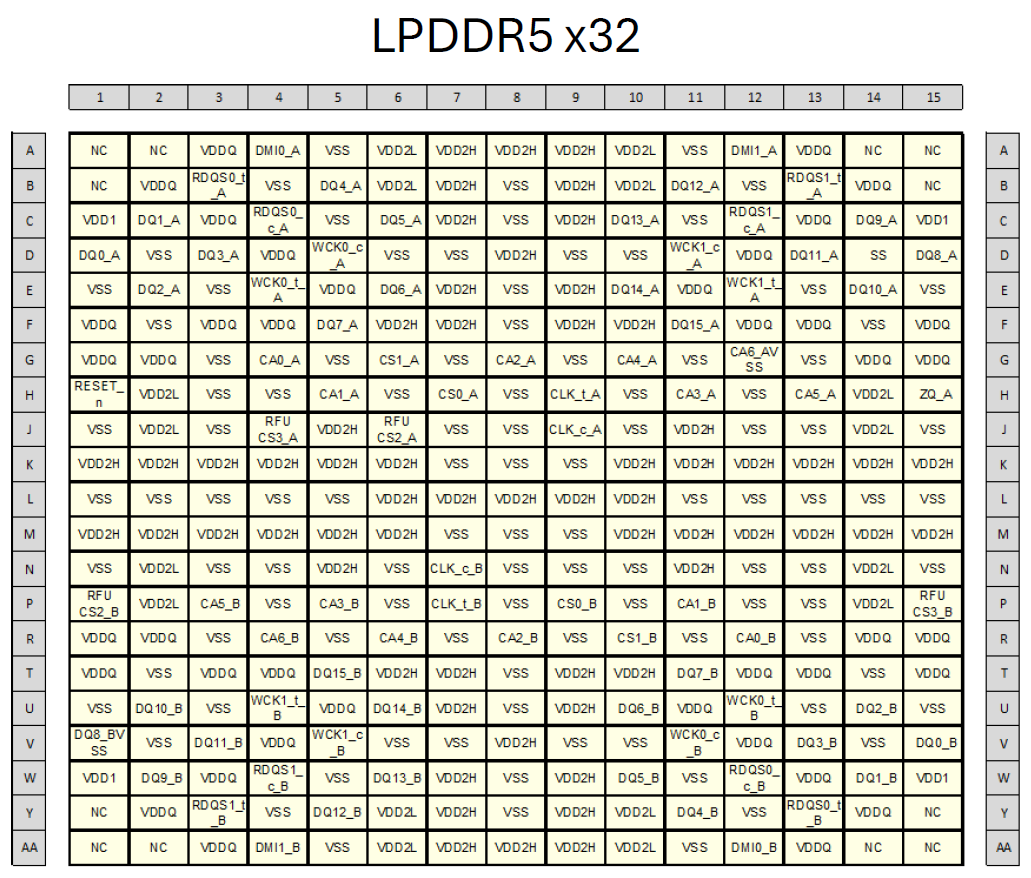

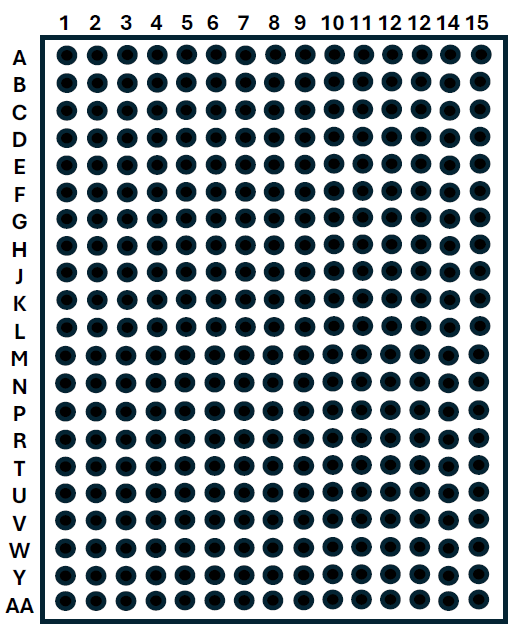

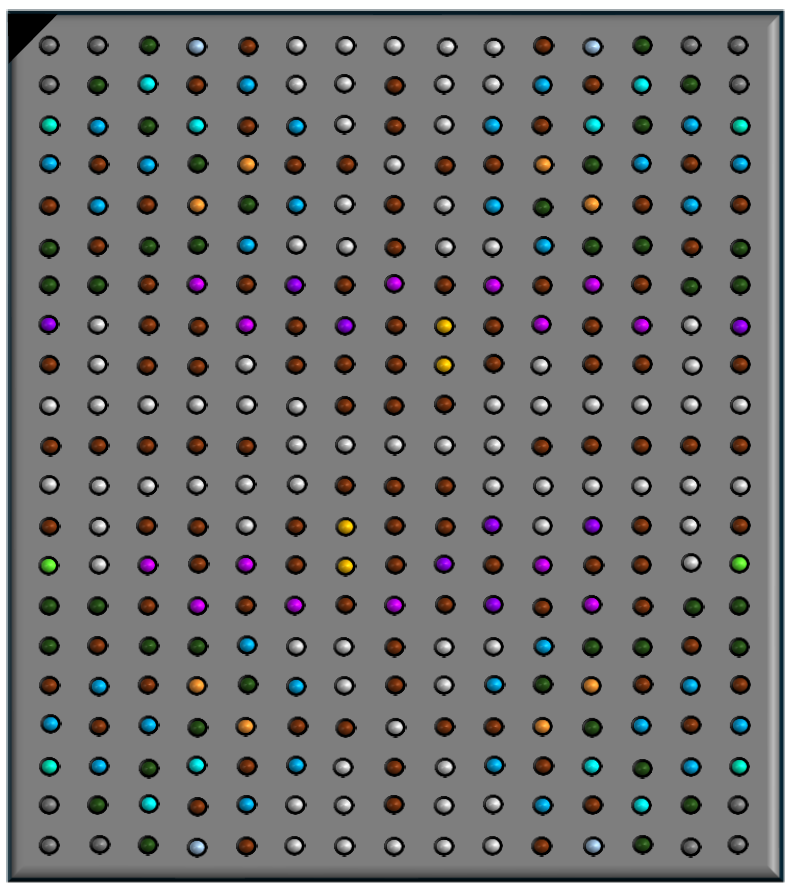

32 位数据位宽的 LPDDR5 封装由 315 个 ball 组成,最大尺寸为 12.4mm x 15mm x 1.1mm。

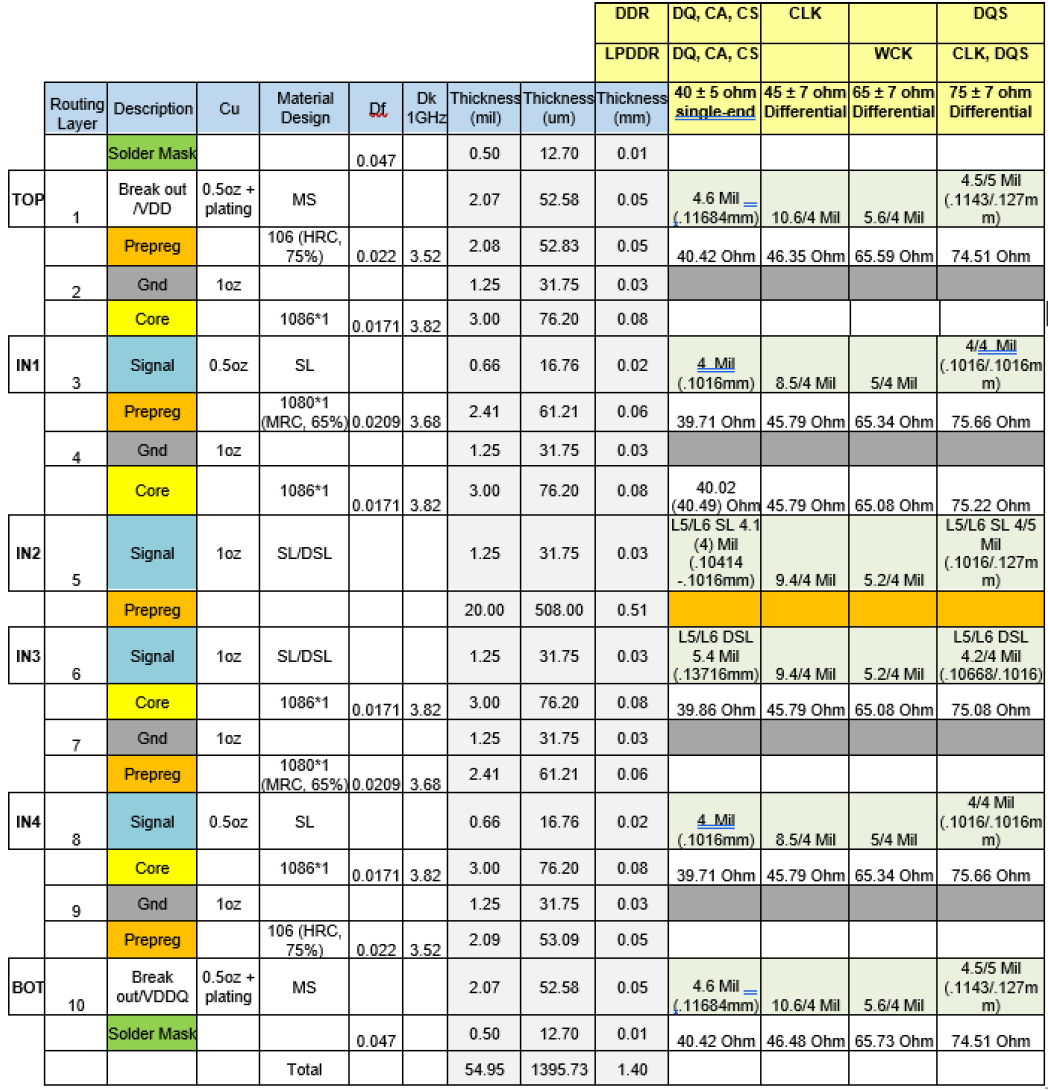

目标阻抗

走线宽度对于匹配目标阻抗非常重要。实际宽度取决于电路板层叠结构。目标是:

DDR5

-

DQ/CA/CS => 40 Ohm

-

DQS => 75 Ohm

-

时钟

-

主板上和模组上到时钟缓冲器:75 Ohm

-

模组上从时钟缓冲器到 DRAM:45 Ohm

-

LPDDR5:

-

DQ/CA/CS => 40 Ohm

-

DQS/CLK => 75 Ohm

-

WCK => 65 Ohm

间距

以下是走线最小间距建议:

-

时钟-时钟

=> .25 mm -

时钟 到 CA

=> .3 mm -

CA 到 CA => .15 mm

-

DQ 到 DQS .18 mm

-

DQ 到 DQ => .18 mm

-

BYTE 到 BYTE => .3 mm

-

WCK 到 DQ => .375 mm

-

WCK 到 DQS => .375 mm

-

子通道 到 子通道 => .5 mm

线长匹配(DDR Memory Down)

-

时钟到时钟:一个通道中的所有时钟

-

时钟到数据选通 (DQS)

-

数据(DQ) 到 DQS

-

一个字节内的 DQ

-

命令地址 (CA) 线到钟

-

一个子通道内的 CA 线

-

片选(CS) 到时钟

-

一个子通道内的 CS 线。

总线长匹配所需的额外数据:

-

芯片供应商提供的 SoC 封装长度(焊盘到Die)

-

打开 Electrical Z Axis Delay 选项

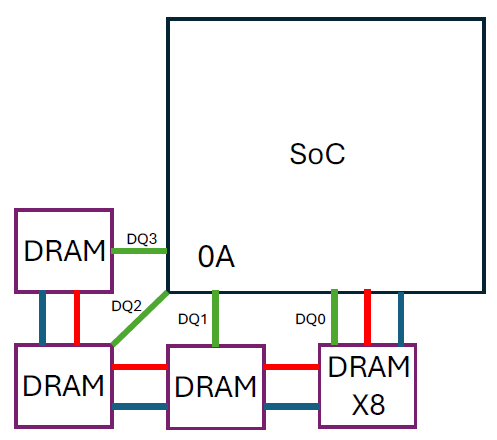

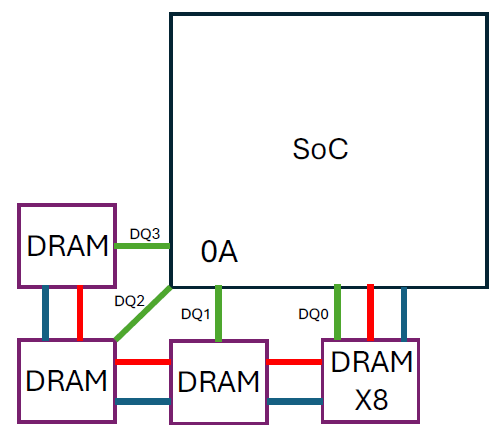

以下是单通道 1 个子通道 0A 的配置示例:

每个子通道包含以下信号:

-

13 CA/4CS(蓝色)

-

时钟(红色)

-

每个DRAM 24 Data/4 DMI/4 DQS/8DQ/1 DMI/1 DQS(绿色)

可能的长度匹配规则:

-

时钟到 CA < 10mm

-

DQ-DQS < 0.5mm

-

DQx8 < 0.5mm

-

每个子通道的 CA < 1 mm

以下是调线长和过孔高度影响的布线技巧

-

在 2 个相邻层上走所有 CA 线

-

在同一层上走所有 DQ, DMI 和 DQS

-

保持时钟线最短 – 它们决定一切

-

检查封装长度 - 它们可能会破坏调线长的计划。

-

注意规则,例如 (-20 < CLK-DQS) < 40)。举个例子,如果时钟是

60 mm , DQS 长度可以在 80 mm 和 20 mm 之间。

线长匹配(LPDDR5 Memory Down)

-

时钟到时钟 - 所有子通道时钟

-

时钟到 DQS

-

DQ 到 DQS

-

一个字节内的 DQ

-

CA 线到时钟

-

一个子通道内的 CA 线

-

CS 到 时钟

-

一个子通道内的 CS 线。

-

写时钟 (WCK) 到 DQ

-

WCK 到 时钟

以下是单通道,4个子通道 0A/0B/0C/0D 的配置示例:

每个子通道包含以下信号信号:

-

7 CA/4CS

-

时钟

-

16 Data/2 DMI/2 DQS

-

2 WCK

可能的长度匹配规则

-

时钟 到 CA < 5mm

-

时钟 到 WCK < 10 mm

-

DQ-DQS

< 3 mm -

DQx8 < 4mm

-

每个子通道的 CA < 7 mm

以下是调线长和过孔高度影响的布线技巧

-

在同一层上布线所有 CA 线

-

在同一层上布线所有 DQ, DMI 和 DQS

-

保持时钟线短 – 它们决定一切

-

检查封装长度 - 它们可能会破坏调线长的计划。

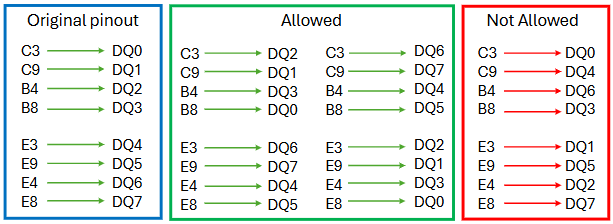

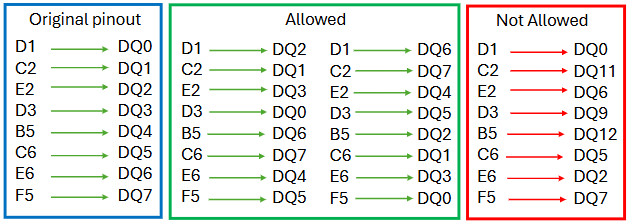

DDR5 引脚交换(Pin Swapping)

DDR5 Layout 中允许进行一些位交换。字节分为 2 个半字节 (nibble):高位和低位。

例如:在位宽为 8 的器件上:

引脚 C3, C9, B4 和 B8 是分配给 DQ[0-3] 的低位;引脚 E3, E9, E4 和 E8 是分配给 DQ[4-7] 的高位。

每个半字节中的位可以在其内部交换。您也可以交换整个半字节,只要同组的 4 个网络保持在同一个半字节中。下图中绿色框是可以交换的示例,红色框因为网络不在同一个半字节中,因此不允许交换。

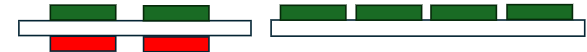

LPDDR5 引脚交换(Pin Swapping)

LPDDR5 layout 中允许进行一些位交换。

-

字节内的任何位都可以交换

-

不允许在字节之间交换

-

可以在子通道内交换整个字节 (包括 WCK, DQS, DMI 和所有 DQ 线)

-

如果可以使布线更整洁,可以交换整个子通道。

以下为可交换及不可交换的示例:

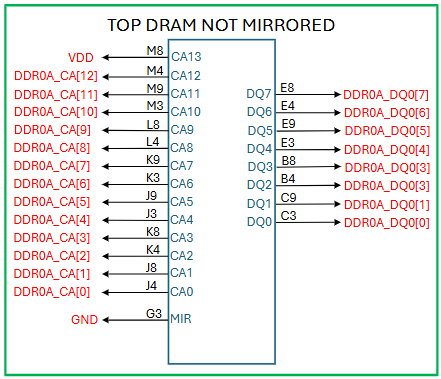

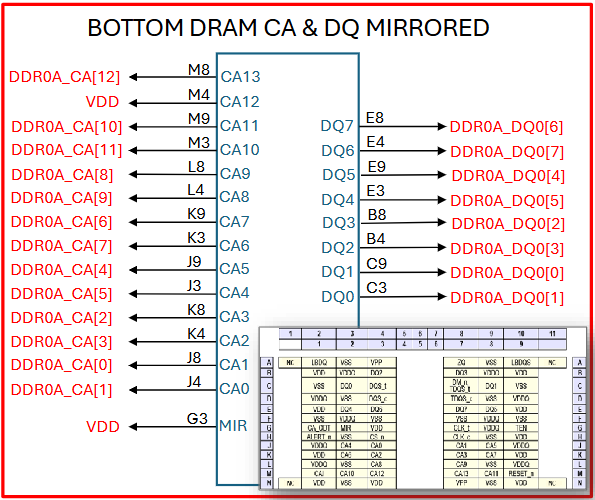

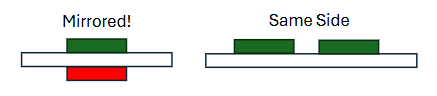

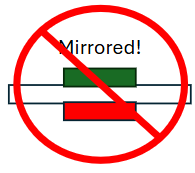

DDR5 镜像(Mirroring)

当 MIR 引脚连接到 VDD 时,DDR5 DRAM 会被镜像。CA 和 DQ 网络需要被镜像。要进行镜像,交换 SoC 网络 CA[0] 和 CA[1]、CA[2] 和 CA[3]、CA[4] 和 CA[5]、CA[6] 和 CA[7]、CA[8] 和 CA[9]、CA[10] 和 CA[11],以及 CA[12] 和 VDD。

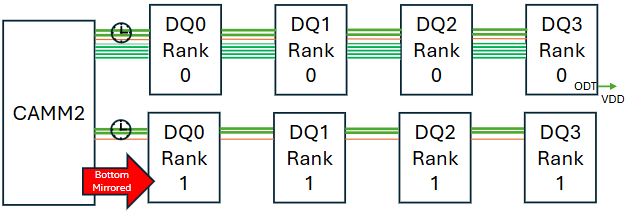

顶层没有镜像的 DRAM:

底层 DRAM CA 及 DQ 被镜像:

LPDDR5 无法配置镜像。

DDR5 拓扑(Topologies)

讲拓扑前再明确一下 Channel(内存通道)、Subchannel(子通道)、Rank(内存列)定义和功能。

Channel(内存通道)

Channel 是 CPU 内存控制器与内存模组(DIMM,即内存条)之间的最高级别数据总线。当我们说一个 CPU 支持“双通道”(Dual-Channel)或“四通道”(Quad-Channel)时,指的是 CPU 有多少条这样独立的主高速公路。在 DDR4 时代,一个 Channel 对应一条 64-bit(不含ECC)的数据总线。在 DDR5 中,一个 Channel 依然是64-bit宽。例如,一个“双通道”CPU(如桌面i9 或 Ryzen 9)就拥有一个128-bit(2 x 64-bit)的内存接口。

Subchannel (子通道)

这是 DDR5 最核心的架构变革。DDR5 将每条 64-bit的 Channel(主通道)拆分成了两个独立的 32-bit 的 Subchannel(子通道)。如果包含 ECC(错误校验码),那么一个 64-bit 的 Channel 被分为两个 40-bit 的 Subchannel(32-bit 数据 + 8-bit ECC)。这两个 32-bit 的 Subchannel 是独立寻址和独立操作的,它们有各自的地址/命令总线。与 DDR4 相比,表面看都是获取 64 字节,但 DDR5 的优势在于它有两个32-bit子通道。当 Subchannel A 在忙于一个请求时,内存控制器可以立即向 Subchannel B 发送另一个完全独立的请求。

Rank (内存列)

Rank 是一组物理 DRAM 芯片(内存颗粒)的集合,这些芯片共享同一个片选信号(Chip Select, CS),并共同组成了 Subchannel 所需的数据位宽。在DDR5中,一个 Subchannel 是 32-bit 宽。如果一根内存条使用的是x8(8-bit位宽)的内存颗粒,那么一个 Rank 就需要4个这样的颗粒(4 x 8 bits = 32 bits 来喂饱一个 Subchannel。

“Single-Rank (1R)” DIMM 通常意味着它为每个 Subchannel 提供了1个 Rank。对于使用 x8 颗粒的 DIMM,它总共需要 4 (SubCh A + 4 (SubCh B) = 8 个颗粒。

“Dual-Rank (2R)” DIMM 意味着它为每个 Subchannel 提供了 2 个 Rank。它总共需要 8 (SubCh A) + 8 (SubCh B) = 16 个颗粒。

单 Subchannel 单 Rank x 16 DRAM

对于单个子通道,1个 Rank,16 位的 DRAM,需要 2 个颗粒。可以同侧或两侧摆放:

2 个 DRAM:

-

有独立的数据总线

-

连接同一个 CLK、CS

-

仅共享 CA 总线

-

CA、CS 和 CLK 采用菊花链拓扑(Daisy chain)

-

1 个 ODT 引脚连接到 VDD 以表示子通道的末端

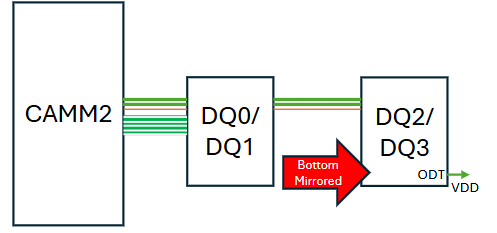

单 Subchannel 单 Rank x 8 DRAM

对于单个子通道,1个 Rank,8 位的 DRAM,需要 4 个颗粒。可以同侧或两侧摆放:

4 个 DRAM:

-

有独立的数据总线

-

连接同一个 CLK、CS

-

仅共享 CA 总线(两侧的情况 CA 可以镜像)

-

CA、CS 和 CLK 采用菊花链拓扑(Daisy chain)

-

1 个 ODT 引脚连接到 VDD 以表示子通道的末端

单 Subchannel 双 Rank x 8 DRAM

对于单个子通道,2个 Rank,8 位的 DRAM,需要 8 个颗粒。

DRAM:

-

分别在顶层、底层两侧

-

共享数据总线

-

共享 CA 总线

-

CA、CS 和 CLK 采用菊花链拓扑(Daisy chain)

-

每个 rank 有独立的 CLK、CS

-

4 个 DRAM 连接到顶层的 CLK0 和 CS0

-

4 个 DRAM 连接到底层的 CLK1 和 CS1

-

-

1 个 ODT 引脚连接到 VDD 以表示子通道的末端

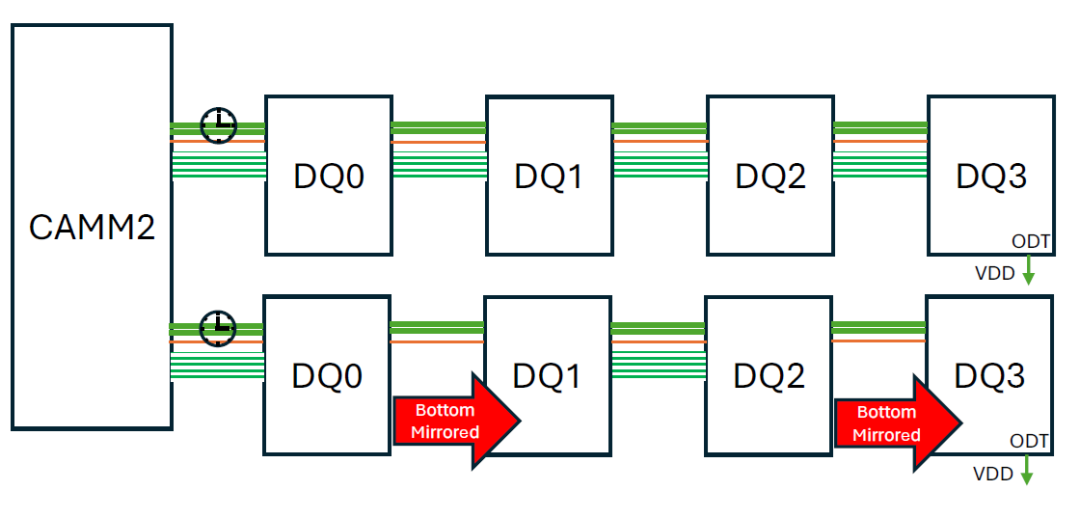

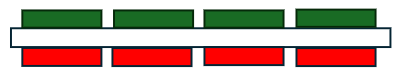

单 Channel 4 Rank x 8 DRAM

对于单个通道,4 个 Rank,8 位的 DRAM,需要 8 个颗粒。

-

DRAM 分别在顶层、底层两侧

-

共享数据总线

-

共享 CA 总线

-

CA、CS 和 CLK 采用菊花链拓扑(Daisy chain)

-

每个 rank 有独立的 CLK、CS

-

镜像 DRAM

-

Rank 0 和 1 被镜像并共享 CA 和 DQ 线

-

Rank 2 和 3 被镜像并共享 CA 和 DQ 线

-

CA 线是菊花链和 T 型拓扑的结合

-

DQ 线可以是菊花链或 T 型拓扑

-

ODT 在 Rank 0 和 Rank 2 的末端连接到 VDD

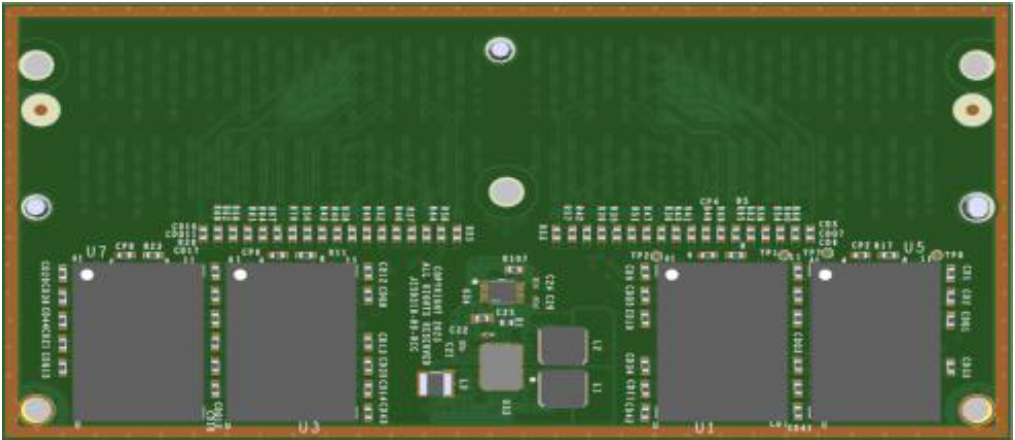

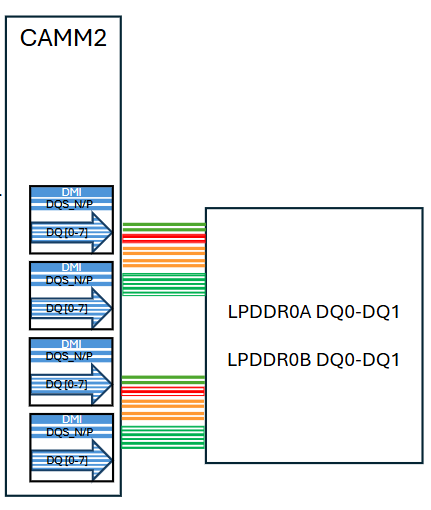

LPDDR5 拓扑

16 位单 Channel DRAM

来自 CAMM2 的每颗 DRAM 4 个数据字节,不可镜像。

-

DRAM 全部位于一侧

-

独立的数据线 - 每个子通道 16 条

-

启用 DMI

-

双子通道

-

每个子通道 7 条 CA 线

-

4 条 CS 线 (如果需要)

-

8mm 间距 – 适用于 BB Via 配置和盘中孔

去耦电容

|

电压 |

指南 |

备注 |

|

VDD |

每颗 SDRAM 至少两个到 VSS 的去耦电容,建议每颗 DRAM 平均 30uF |

应尽可能靠近 DRAM VDD 焊球 |

|

VDDQ |

每颗 SDRAM 至少两个到 VSS的去耦电容,建议每颗 DRAM 平均 7.5uF |

应尽可能靠近 DRAM VDDQ 焊球 |

|

VPP |

每个 DRAM VPP 引脚至少一个去耦电容,建议每颗 DRAM 平均 3.5uF |

应尽可能靠近 DRAM VPP 焊球 |

|

VIN_BULK |

PMIC 输入附近:6 颗 22uf, 3 颗 0.1uF CAMM2 连接器 VIN_BULK 引脚附近:4 颗 22uF 或 0.1uF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PMIC 输入附近:8 颗 22uf, 4 颗 0.1uF CAMM2

连接器 VIN_BULK 引脚附近:6 颗 0.1uF

|

|

|

1. VDD, VDDQ 和 VPP 的去耦电容值因模组而异,并可能交错以实现最佳的整体阻抗 vs 频率响应。 |

||

|

2. VDD, VDDQ 和 VPP 的推荐去耦值为 1uF, 22uF, 4.7uF 和 10uF。 |

||

|

3. 根据 DRAM 封装尺寸,可能无法实现所有布局。 |

||

|

4. 有关 PMIC 芯片周围去耦的详细信息,请参阅 PMIC 规格。 |

||